Effective Layer Stackup Strategies in PCB Design

24 Jun 2025 14:41:30 GMT

PCBASAIL

24 Jun 2025 14:41:30 GMT

PCBASAIL

Have you ever stared at a stack of copper-clad boards and wondered, “How many layers do I really need for this design?” When it comes to multilayer PCBs, choosing the right layer count and stackup isn’t just a manufacturing detail—it’s one of the biggest factors that determines how well your board handles complexity, fits into a tight enclosure, and keeps electromagnetic emissions in check.

Why Layer Count Matters

Before you fire up your CAD tool, you’ve got to ask yourself three key questions:

Circuit complexity & density

Board size & shape

Electromagnetic compatibility (EMC) requirements

Do you need just enough copper to route a handful of signals, or are you packing hundreds of nets—including delicate high-speed pairs—into a small footprint? A simple two-layer board might be cheap, but the moment you push trace widths, suffer crosstalk, and struggle to fit differential pairs, you’ll regret not going to four or six layers.

Once you pick a layer count—4, 6, 8, or more—the next step is deciding where each layer goes: which ones carry power, which ones carry ground, which ones carry critical signals, and how those layers stack up. That stackup is your first line of defense against EMI (electromagnetic interference) and signal-integrity nightmares.

Factors in Choosing Your Stackup

Routing vs. Cost & Complexity

More layers = more routing freedom. If you’ve ever cursed at yourself trying to snake a trace between BGA balls on a two-layer board, you know the pain.

But more layers = higher cost & tighter tolerances. Manufacturers have to press, drill, and plate each layer, so your price goes up. And asymmetric stackups can warp the board if you’re not careful.

Symmetry & ManufacturingPCB

shops love symmetric builds because they press evenly and stay flat. If you do a 4-layer board, you might mirror layer 1/2 over layer 3/4 so the board “looks” the same top-to-bottom. That helps prevent bow and twist during lamination.

EMC Requirements

EMC performance is directly tied to how your power and ground planes sandwich your signal layers. A layer with no neighboring reference plane becomes an island that can’t contain return currents, so you get bigger loops, more radiation, and dirty signals.

Experienced designers typically follow a smart sequence:

Component placement—lay out all the chips, connectors, and components roughly where they’ll go.

Identify routing bottlenecks—see where BGAs, fine-pitch parts, or high-speed nets will squeeze you.

Run your EDA tool’s density analysis—plot hot spots of trace congestion.

Count your special nets—differential pairs, analog inputs, high-speed clocks—and earmark a signal layer for them.

Tally your power rails—figure out which voltages you need, and whether any nets require isolation or extra filtering.

Decide how many internal plane layers you need (ground/power layers) to support those signals.

By the end of that exercise, you’ll have a pretty solid idea: “Yep, this baby needs six layers, with two planes and four signal layers.”

Two Golden Rules of Stackup Design

No matter how many layers you pick, always follow these two gospel truths:

Every routing layer needs a nearby reference plane (power or ground). That way, return currents can flow with minimal loop area.

Keep adjacent power & ground layers as close together as you can. A thin dielectric between them creates a big distributed capacitance—your board’s built-in decoupling network.

Single- and Double-Layer Boards

If you’re on a one- or two-layer design, you can’t stack internal planes. So EMC control falls back to layout techniques:

Minimize loop area on every critical net. The smaller the loop, the less radiation it emits and the less it picks up.

Keep power & ground traces close together, running in parallel.

Split ground next to sensitive signal lines. A little guard trace can do wonders.

If you have a two-layer board, route a heavy ground trace or plane on the bottom directly beneath your top-side high-speed line. That gives you a tiny loop (board thickness × trace length) to contain your signals.

These tricks let two-layer boards hit decent EMC performance in low-frequency analog or simple digital (<10 kHz) contexts. Beyond that, you’ll be begging for more layers.

Four-Layer Stackups

With four layers, you can finally get an internal plane for power and ground. Two common stackups are:

- Signal – GND – PWR – Signal

- GND – Signal/PWR – Signal/PWR – GND

Signal – GND – PWR – Signal

Pros: Excellent signal-integrity for the outer layers (each has its own plane).

Cons: and power layers sit next to each other in the center, but if your board is the standard 1.6 mm (~62 mil) thick, that midplane separation gets a bit fat—impedance control and shielding suffer.

This arrangement works great when you’ve got a ton of BGAs or dense routing on the outer layers. Just remember to route carefully to manage EMI and maybe add stitching vias to tie power and ground planes together.

GND – Signal/PWR – Signal/PWR – GND

Pros:Outer layers are solid ground planes—stellar shielding. Inner mixed layers carry your signals and power pours.

Cons: The signal/power layers are both “busy,” so you have to micro-manage routing to keep impedance consistent.

From an EMI perspective, this is often the best 4-layer build because your precious signal layers are tucked right up against a ground plane (or at least a solid copper plane). Just watch those mixed inner layers—keep wide power pours for low impedance, run signal traces in the same direction on each inner layer, and space planes to follow the 20 H rule (stackup thickness ≤ 1/20th of a wavelength at your highest frequency of interest).

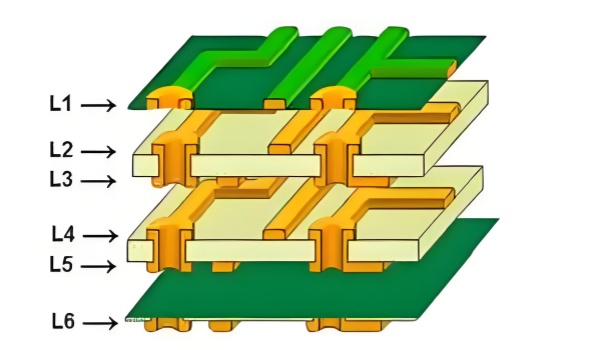

Six-Layer Stackups

If you’re packing lots of nets or pushing clocks into the hundreds of MHz, six layers really start to shine. A popular scheme is:

SIG – GND – SIG – PWR – GND – SIGSignal Integrity: signal layer cuddles up next to a ground plane or power plane, so you get tight impedance control and short return paths.

EMI Control: Two ground planes soak up stray magnetic fields, and pairing a power plane with a ground plane gives you fat, low-impedance decoupling.

Routing: Three signal layers gives you breathing room for differential pairs, BGA escape, and general nets.

Another option for lower component density is:

GND – SIG – GND – PWR – SIG – GNDThat way, your top and bottom are both solid grounds (great for shielding), and your signal/power sandwich is in the middle. Just keep power next to the inner ground for maximum decoupling, and ensure your vias stitch all ground lands together.

Eight-Layer Stackups

At eight layers, you’ve got serious real estate:

Variant 1 (not ideal for EMI): alternating signal & plane layers but with some large plane separations.

Variant 2 (better EMI): add more reference planes so each critical signal layer gets a neighboring ground or power plane.

Ideal scheme: multiple ground planes interleaved with power and signal layers, giving you best-in-class absorption of stray fields and superb impedance control.

Typically your “dream” 8-layer might look like:

| Layer | Description | Type |

|---|---|---|

1 |

Top Layer – Microstrip Signal |

Signal |

2 |

Ground Plane |

Ground |

3 |

Internal Signal Layer – Stripline |

Signal |

4 |

Power Plane (coupled with Layer 5) |

Power |

5 |

Ground Plane |

Ground |

6 |

Internal Signal Layer – Stripline |

Signal |

7 |

Ground Plane |

Ground |

8 |

Bottom Layer – Microstrip Signal |

Signal |

That puts three distinct ground planes around your signal layers, giving you a cage that keeps signals on the straight and narrow and stifles EMI.

How to Pick Your Perfect Stackup

There’s no one-size-fits-all. When deciding how many layers and which stackup to choose, juggle these factors:

Signal count: more nets drive more layers.

Component density: BGAs, QFNs, and fine-pitch parts demand inner layers for escape routing.

Pin density: the more pins per part, the more you need internal routing channels.

Signal speed: MHz-level clocks and multi-Gbps data lines need tight impedance and close ground returns.

Board size: if you need to squeeze a big CPU and memory and analog subsystems, go vertical with more layers.

As a rule of thumb, if your design has high net count, dense BGAs, high pin counts, or signals zipping above a few hundred megahertz, lean toward a multilayer board with a solid ground or power reference next to each signal layer. That way, you’ll hit signal-integrity goals, tame EMI, and get your board through compliance testing without tears.

Final Takeaway

Stackup design is a balancing act of routing freedom, cost, and EMC performance. Follow these basics and you’ll be in good shape:

Always give your signal layer a close reference plane (GND or PWR).

Keep power & ground as close as possible to create distributed decoupling.

Symmetrize your stackup to avoid warpage.

Plan for your worst-case nets early—don’t wait until layout hell to realize you need more layers.

With thoughtful stackup choices, you’ll transform a messy spaghetti-routing nightmare into a clean, quiet, high-performance PCB that just works—first time, every time. Happy designing!